偦傟偱偼丄倁俥俷偺惢嶌傪巒傔傑偡丅帋嶌偟偨儔僟乕僼傿儖僞乕偺拞怱廃攇悢偼丄侾俀丏侽侽侽俆俵俫倸偱偡丅

侾係俵俫倸偺俽俽俛僶儞僪乮侾係丏侾侽侽俵俫倸偐傜忋乯偵弌傞偨傔偵偼

侾係丏侾侽侽亅侾俀丏侽侽侽俆亖俀丏侽俋俋俆俵俫倸丒丒丒彮偟梋桾傪傒偰丄嵟掅敪怳廃攇悢俀丏侽俋俆俵俫倸

壜曄暆侾侽侽俲俫倸傪栚昗偵丄僗僾儕傾僗偺僠僃僢僋傪偟偰傒傑偡丅

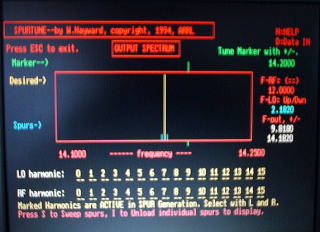

埲慜偼揹戩偱丄俴俷偺俀攞亄俬俥偼偄偔偮偐側丠側偳偲傗偭偰偄傑偟偨偑丄乽俬俼俥俢乿偺僜僼僩僂僃傾乕偺拞偵

僗僾儕傾僗偺僠僃僢僋傪偟偰偔傟傞俽倫倳倰倲倳値倕偲偄偆曋棙側傕偺偑偁傝傑偡偺偱妶梡偟偰傒傑偟偨丅

丂丂

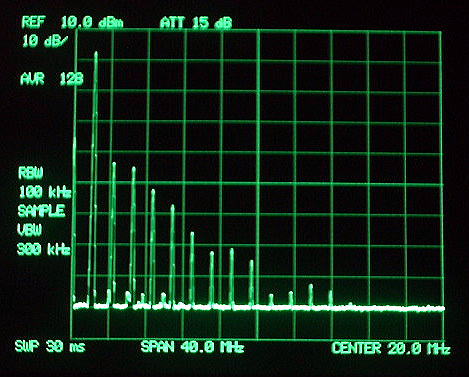

丂丂嵍偼丄俬俥亖侾俀俵俫倸丄倁俥俷傪俀丏侽俋俆俵俫倸偐傜

丂丂俀丏侾俋俆俵俫倸傑偱曄壔偝偣偨帪偺僗僾儕傾僗傪

丂丂僠僃僢僋偟偰偄傞偲偙傠偱偡丅

丂丂俬俥丄倁俥俷嫙偵侾俆攞偺崅挷攇傑偱寁嶼偟偰偔傟傑偡丅

丂丂寢壥偼侾係丏侾俉俀俵俫倸偵弌傞帪丄侾係丏侾俉侽俵俫倸偲

丂丂侾係丏侾俉係俵俫倸偵僗僾儕傾僗偑弌傞傛偆偱偡丅

丂丂

偲偼偄偆傕偺偺丄乮俬俥丂倶丂俁乯亅乮倁俥俷丂倶丂侾侽乯亖侾係丏侾俉侽俵俫倸

丂丂丂丂丂丂 丂丂丂丂乮倁俥俷丂倶丂侾俀乯亅乮俬俥丂倶丂侾乯亖侾係丏侾俉係俵俫倸

偱偡偺偱丄倁俥俷偺崅師崅挷攇偵廫暘拲堄偡傟偽丄俷俲偱偡偹丅

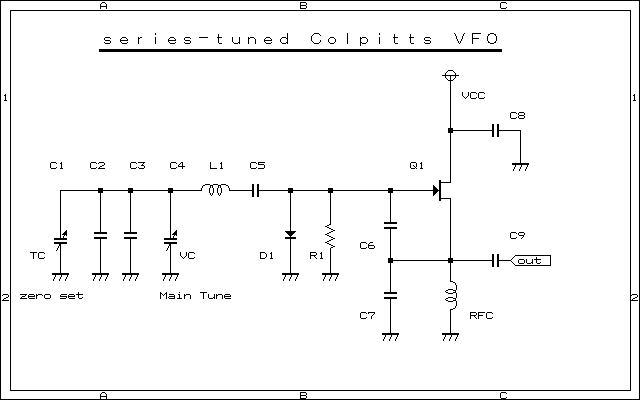

忋婰偑倁俥俷偺敪怳晹偺夞楬恾偱偡丅偙偙偱丄敪怳廃攇悢傪寛掕偡傞僐儞僨儞僒乕偺崌寁梕検偺

寁嶼偼師偺傛偆偵側傝傑偡丅

俴侾偺嵍懁偼慡偰暲楍愙懕偱偡偐傜丄崌寁梕検乮俠倎乯偼丄丂俠倎亖俠侾亄俠俀亄俠俁亄俠係

俠俇偲俠俈偼捈楍粋陚蓚p侾偺擖椡梕検偑暲楍偵壛傢傝傑偡偺偱丄崌寁梕検乮俠倐乯偼

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂俠倐亖乷乮俠俇丂倶丂俠俈乯亐乮俠俇丂亄丂俠俈乯乸亄俇倫俥乮擖椡梕検乯

俠俆偲俠倐偼捈楍愙懕偱偡偐傜丄崌寁梕検乮俠們乯偼丄丂俠們亖乮俠俆丂倶丂俠倐乯亐乮俠俆丂亄丂俠倐乯

嵟屻偵俴侾偺嵍偲塃偱捈楍愙懕偵側傝傑偡偺偱丄崌寁梕検俠倲偼

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂俠倲亖乮俠倎丂倶丂俠們乯亐乮俠倎丂亄丂俠們乯丂

偦傟偱偼丄幚嵺偵寁嶼偟偰傒傑偟傚偆丅俠侾偐傜俠俈傑偱偺抣偼丄埲慜惢嶌偟偨倁俥俷偺抣傪嶲峫偵

俠侾亖侾侽倫俥乮俀係倫俥僩儕儅乕偺栺拞怱乯丄俠俀亖侾俆侽倫俥丄俠俁亖侾俀侽倫俥丄俠係亖俆侽倫俥乮僶儕僐儞乯

俠俆亖俁俋侽侽倫俥丄俠俇仌俠俈亖侾俀侽侽倫俥偲偟偰傒傞偲

僶儕僐儞乮俠係乯梕検嵟戝帪丂丂丂俠倲亖俀侽俀丏俆倫俥

丂丂丂丂丂丂丂丂丂丂丂丂嵟彫帪丂丂丂俠倲亖侾俉俀丏俆倫俥

偝傜偵丄晜梀梕検偑壛傢傝傑偡偺偱丄俠倲乮嵟戝乯亖俀侾侽倫俥丄俠倲乮嵟彫乯亖侾俋侽倫俥丂偲偟傑偡丅

偦傟偱偼丄妝偟偄僐僀儖姫偒偵恑傒傑偡丅偱傕丄偦偺慜偵僀儞僟僋僞儞僗偺寁嶼傪丅

俠倲乮嵟戝乯亖俀侾侽倫俥偱俀丏侽俋俆俵俫倸傪敪怳偝偣傞偵偼丄俴侾亖俀俈丏俆兪俫偲側傝傑偡丅

偦偟偰丄俀俈丏俆兪俫偲俠倲乮嵟彫乯亖侾俋侽倫俥偱敪怳偝偣傞偲丄俀丏俀侽俵俫倸偵側傝傑偡偐傜

寁嶼忋偼丄侾侽俆俲俫倸壜曄偝偣傞帠偑偱偒傞偙偲偵側傝傑偡丅

師偵丄巊梡偡傞僩儘僀僟儖丒僐傾偱偡偑丄傾儈僪儞偺俿亅俇俉亅俀偵偟傑偟偨丅

偲偙傠偱丄偄傠偄傠側惢嶌婰帠傪撉傓偲丄倁俥俷偺僐傾偵偼嵽幙仈俇傪悇慐偟偰偄傑偡丅

偙傟偼丄仈俇嵽偺壏搙學悢偑亄俁俆倫倫倣乛亷偲偡偖傟偰偄傞偨傔偱偡丅

偪側傒偵丄仈俀嵽乮俿亅俇俉亅俀乯偺壏搙學悢偼亄俋俆倫倫倣乛亷偱丄仈俇嵽傛傝

埆偄偺偱偡偑丄夞楬偵僗僠儘乕儖丒僐儞僨儞僒乕乮壏搙學悢偑乕侾侽侽倫倫倣乛亷偐傜

亅俀侽侽倫倫倣乛亷乯傪巊偆偲丄憡嶦偟偁偭偰丄戝曄丄埨掕搙偺椙偄倁俥俷偵側傝傑偡丅

偝偰丄俿亅俇俉亅俀偱俀俈丏俆兪俫傪摼傞偨傔偵偼丄慄傪俈侽夞姫偐側偗傟偽側傝傑偣傫丅

侽丏俁俀倣倣偺慄傪侾係侽們倣偺挿偝偵愗偭偰丄儔僕僆偺壒妝斣慻傪暦偒側偑傜

姫偄偰偄偨傜丄係俆暘傕偐偐傝傑偟偨丒丒丒丒丒崱擔偼偙傟偱廔傢傝偵偟傑偡丅

僩儘僀僟儖丒僐傾偵慄傪姫偔帪丄偒偭偪傝姫偔偨傔偵丄慄傪傂偭傁傝側偑傜姫偒傑偡丅

偙傟偑慄嵽偵僗僩儗僗偲側傝丄屻乆偺倁俥俷偺埨掕搙偵塭嬁偟偰偒傑偡丅夝寛曽朄偲偟偰

僐僀儖傪儃僀儖偡傞偲椙偄偲丄偁傞俫俹偵婰嵹偝傟偰偄傑偟偨丅

偦偙偱崱擔偼丄撶偵偨偭傉傝搾傪暒偐偟偰丄俇暘娫僐僀儖傪椏棟偟偰傒傑偟偨丅

偨偩偟丄僐僀儖偼嵷偽偟偱帩偭偰丄撶掙偵怗傟側偄傛偆偵偟傑偡丅

俇暘偨偭偨傜丄廔椆丅屻偼帺慠椻媝偝偣傑偡丅偄傛偄傛師偼丄倁俥俷偺帋嶌偱偡丅

崱擔偼惗婎斅忋偵夞楬傪僶儔僢僋嶌傝偟偰傒傑偟偨丅嵟弶偼俀楢僶儕僐儞偺曅懁乮係侽倫俥乯偱

帋偟偨強丄廃攇悢偺壜曄暆偑俇俉俲俫倸偟偐偲傟側偔偰丄椉曽乮俉侽倫俥乯巊偆偙偲偵偟傑偟偨丅

偙傟偵傛傝壜曄暆偑侾俀俁俲俫倸偲側傝丄侾係丏侾侽侽俵俫倸偐傜侾係丏俀侾俉俵俫倸傑偱弌傟偦偆偱偡丅

側偍丄僶儕僐儞偺梕検傪憹傗偟偨偨傔丄俿亅俇俉亅俀偺姫悢偼俇俉僞乕儞偵曄峏偟傑偟偨丅

偝偰丄廃攇悢埨掕搙偱偡偑丄僐乕儖僪僗僞乕僩屻侾侽暘娫偼亇俆俫倸撪偱傆傜傆傜偟偰偄傑偡偑

偦偺屻偼備偭偔傝壓偑偭偰偄偒傑偡丅嵟弶偺廃攇悢偐傜侾帪娫屻偱乕侾俉俫倸丄俀帪娫屻偱亅俀俇俫倸

偱偟偨丅偙傟偔傜偄偺僪儕僼僩側傜丄埨怱偟偰俽俽俛偱儔僌僠儏僂偱偒傑偡偹丅

師偼丄婎斅偵慻傫偱僔乕儖僪働乕僗偵廂傔丄僗僾儕傾僗摍偺僠僃僢僋傪偟傑偡丅

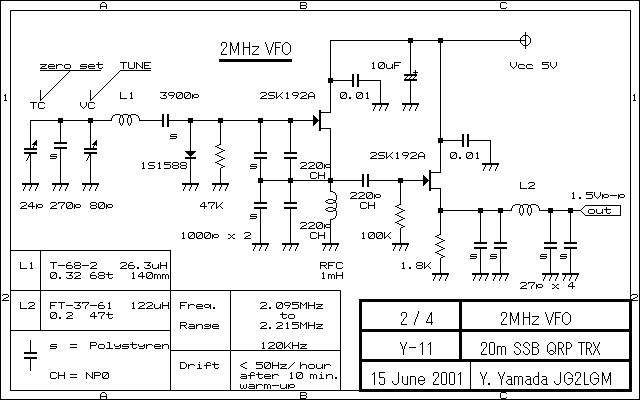

忋婰偼倁俥俷偺夞楬恾偱偡丅敪怳偍傛傃僶僢僼傽偵偼愙崌宆俥俤俿偺俀俽俲侾俋俀俙乮俧俼乯傪巊梡偟偰偄傑偡丅

夞楬恾偺僐儞僨儞僒乕偺乵倱乶偼僗僠僐儞丄俶俹侽乮僱僈僥傿僽丒億僕僥傿僽丒僛儘偺棯乯偼僙儔僐儞偱

壏搙學悢亇侽乮僐儞僨儞僒乕偺摢偑崟偔揾偭偰偁傞乯傕偺偱偡丅敪怳晹偺俀俽俲侾俋俀俙乮俧俼乯偺僎乕僩偺

侾侽侽侽倫俥偺僗僠僐儞偲俀俀侽倫俥偺俶俹侽偼暲楍偱偡偐傜崌寁梕検侾俀俀侽倫俥偵側傝傑偡丅偙偺慻傒崌傢偣傪

曄偊傞偲乮椺偊偽丄俀侽侽倫俥偺僗僠僐儞偲侾侽侽侽倫俥偺俶俹侽偺慻崌偣偲偐丄侾俀侽侽倫俥偺僗僠僐儞偩偗偲偐乯

廃攇悢曄摦偺巇曽偑旝柇偵曄壔偟傑偡偺偱丄幚尡偟偰儀僗僩偺慻崌偣偵偡傞偲椙偄偲巚偄傑偡丅

偝偰丄倁俥俷偺廃攇悢埨掕搙傪崅偔偡傞偨傔丄愄偐傜傛偔尵傢傟偰偄傞丄僔乕儖僪丒働乕僗偵廂傔傞丄埨掕壔

偝傟偨揹尮傪巊梡偡傞丄偲偄偆偺偼摉慠偲偟偰丄懠偵傕

丂仏敪怳夞楬偵偼愙崌宆俥俤俿傪巊偄丄僎乕僩偵僔儕僐儞丒僟僀僆乕僪傪擖傟傞丅

丂仏敪怳廃攇悢旝挷惍梡偺僩儕儅丒僐儞僨儞僒乕偼僙儔儈僢僋偱偼側偔丄僄傾丒僶儕偺暔傪巊偆丅

丂仏僩儘僀僟儖丒僐傾偼姫偒慄偟偨屻丄儃僀儖偟偰帺慠椻媝偝偣傞丅

丂仏僩儘僀僟儖丒僐僀儖偺婎斅傊偺屌掕偵偼僾儔僗僠僢僋丒僱僕傪巊偆丅僐僀儖傪墴偝偊傞偺傕僾儔僗僠僢僋惢偺

丂丂壓晘偒摍傪墌偔愗偭偨暔傪巊梡偟丄僱僕偼寛偟偰嫮偔偟傔偰偼偄偗傑偣傫丅巜偱偐傞偔偝傢偭偰摦偐側偄掱搙

丂丂偱俷俲偱偡丅嫮偔偟傔傞偲丄慄嵽偵僗僩儗僗傪偁偨偊丄僪儕僼僩偺尨場偵側傝傑偡丅

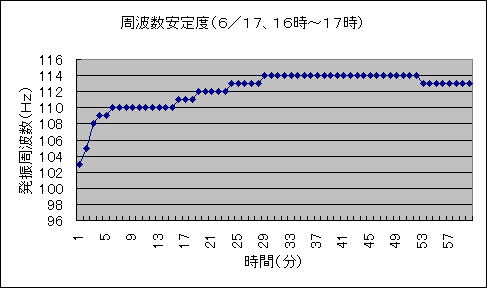

忋婰偼僐乕儖僪丒僗僞乕僩屻侾帪娫偺廃攇悢埨掕搙傪悢夞應掕偟偨拞偱嵟傕埨掕搙偺椙偐偭偨帪偺僨乕僞偱偡丅

偄傢備傞僠儍儞僺僆儞丒僨乕僞偱偡偹丅敪怳廃攇悢乮俫倸乯侾侽侽偼俀丆侾俁侽丆侾侽侽俫倸傪帵偟傑偡丅

僐乕儖僪丒僗僞乕僩屻侾帪娫偱亄侾侽俫倸偺曄摦偱偡偐傜丄側偐側偐俥俛偱偡偹丅

廃埻壏搙乮幒壏乯偑堦掕側傜嬌傔偰埨掕搙偺崅偄倁俥俷偵側傝傑偟偨丅

忋偺幨恀偼僶僢僼傽丒傾儞僾俀俽俲侾俋俀俙乮俧俼乯偺僜乕僗弌椡偺僗僾儕傾僗偱偡丅戞俀崅挷攇偼亅俁俇倓俛偱

僗僾儕傾僗偼侾係攞攇傑偱傒偊傑偡丅偱傕丄僆僔儘偱偙偺攇宍傪尒傞偲丄傢傝偲偒傟偄側惓尫攇偵尒偊偰偟傑偄傑偡

偺偱拲堄偟傑偟傚偆丅忋婰偺倁俥俷偺夞楬偱偼丄偙偺僗僾儕傾僗傪墴偝偊傞偨傔偵俴俹俥傪擖傟偰偁傝傑偡丅

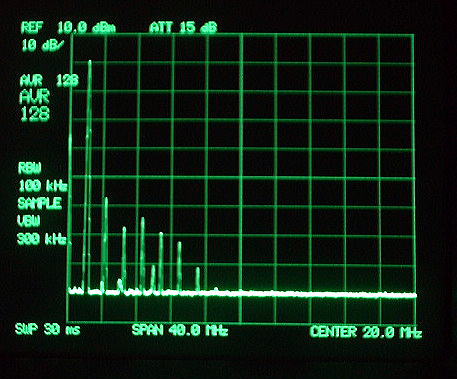

忋偺幨恀偼倁俥俷偺弌椡偺僗僾儕傾僗偱偡丅戞俀崅挷攇偼亅係俉倓俛偱丄妋擣偱偒傞崅挷攇偼俉攞攇傑偱偱偡丅

僜乕僗弌椡偺幨恀偲斾傋傞偲椙偔傢偐傝傑偡偑丄俴俹俥偺岠壥偼戝偒偄偱偡偹丅

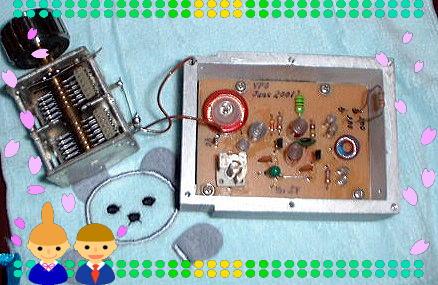

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂 嵍偼姰惉偟偨倁俥俷偱偡丅働乕僗偼傾儖儈

嵍偼姰惉偟偨倁俥俷偱偡丅働乕僗偼傾儖儈

丂丂僟僀僉儍僗僩偱丄昹徏偺僴儉丒僼僃傾偱

丂丂擖庤偟偨傕偺偱偡丅僶儕僐儞偼墶昹偺

丂丂僴儉丒僼僃傾偱峸擖偟傑偟偨丅

丂丂

丂丂幨恀偱偼丄僶儕僐儞偲婎斅娫傪嵶偄慄偱

丂丂攝慄偟偰偁傝傑偡偑丄幚憰帪偵偼

丂丂懢偄乮侾倣倣埲忋乯偺扨慄偱攝慄偟傑偡丅

丂丂丂

丂丂嵶偄慄偱偡偲丄傆傜傆傜偟偰僪儕僼僩偺

丂丂尨場偵側傝傑偡偺偱梫拲堄偱偡丅

憗偄傕偺偱丄倁俥俷傪嶌傝巒傔偰偐傜敿擭偑夁偓偰偟傑偄傑偟偨丅偙偺儁乕僕傪偛棗偵側偭偰丄偄傑偝傜俴俠偺倁俥俷

側傫偰偲巚傢傟傞曽傕懡偄偲巚偄傑偡丅俁擭慜偵俀侾俵俫倸偺俽俽俛僩儔儞僔乕僶乕傪惢嶌偟丄儘乕僇儖偺媄弍壆偝傫

偵尒偣偨傜丄乽俴俠偺倁俥俷側偺丠偦傫側偺丄俬俠丄侾屄偱俷俲偩傛丅乿偲尵傢傟偰偟傑偄傑偟偨偐傜丅

偨偟偐偵崱偼俢俢俽偺帪戙偱偡偐傜丄敪怳廃攇悢偼僪儕僼僩偟側偄偺偑摉偨傝慜丅偦傫側帪戙偱偡偐傜

媡偵丄彮偟僪儕僼僩偡傞偺傕丄傾儅僠儏傾偺庤嶌傝偺枴偑偟偰丄側偐側偐椙偄偺偱偼偲巚偭偰偄傑偡丅